## Self-aligned TiSi<sub>2</sub>/Si heteronanocrystal nonvolatile memory

Yan Zhu, Dengtao Zhao, Ruigang Li, and Jianlin Liu<sup>a)</sup>

Quantum Structures Laboratory, Department of Electrical Engineering, University of California, Riverside, California 92521

(Received 31 May 2005; accepted 1 February 2006; published online 9 March 2006)

The titanium silicide/silicon (TiSi<sub>2</sub>/Si) heteronanocrystals are fabricated on SiO<sub>2</sub> thin films. The metal-oxide-semiconductor structure embedding the TiSi<sub>2</sub>/Si heteronanocrystals shows superior performance over the Si dot device. The charge loss rate in the TiSi<sub>2</sub>/Si heteronanocrystal device is 7.5 times less than that of the Si dot device. It is also found that the TiSi<sub>2</sub>/Si heteronanocrystal device has wider memory window than the Si dot counterpart. © 2006 American Institute of Physics. [DOI: 10.1063/1.2183815]

Due to the discrete nature, Si nanocrystals in a metaloxide-semiconductor (MOS) field-effect-transistor structure as the floating gates possess a promising future and have been extensively investigated since it was pioneered by Tiwari *et al.*<sup>1</sup> Besides Si nanocrystals, tremendous effort has also been made to exploit new kinds of nanocrystal floating gate, such as Ge nanocrystals,<sup>2</sup> metal,<sup>3-6</sup> or metallike<sup>7</sup> dot and dielectric nanocrystals (Al2O3, HfO2, Si4N3, etc.).8-10 Intrinsically, semiconductor nanocrystals encounter the issue that the large amount of defect-induced charge traps play important roles in the memory mechanism due to the relatively small density of states of the nanocrystals. Therefore, the annealing treatment of the device can dramatically change the device performance, which in other words means the thermal instability of the device. The situation remains for the dielectric nanocrystals since the defect-induced traps are now the only mechanism for charge retention. Furthermore, the higher defect levels also induce the erasing saturation as has been found in the silicon-oxide-nitride-oxidesilicon memory device.<sup>11</sup> A feasible solution to rule out the defect effect is to employ nanocrystals with high density of states, such as metal nanocrystals.<sup>3-6</sup> One concern of using some metal nanocrystals is the possible reaction between the oxide and the metal during the annealing processes for the metal dot formation. To solve this issue, recently the metallike TiN nanocrystals have been reported<sup>7</sup> which exhibits good thermal ability of the nanocrystals.

In this letter, we report the MOS memory device using  $TiSi_2/Si$  heteronanocrystals as the floating gates. Due to the self-alignment nature of the  $TiSi_2$  on Si, the  $TiSi_2/Si$  heteronanocrystals can be readily fabricated based on Si nanocrystals. The work function difference between  $TiSi_2$  and Si and additional barrier of Si for charges in  $TiSi_2$  help the data retention and rule out the effect from defect-related shallower-level traps inside the nanocrystals and at the interface of nanocrystal/oxide.

A chemically cleaned 4 in. *p*-type Si wafer with doping concentration of  $5 \times 10^{15}$  cm<sup>-3</sup> is oxidized at 1000 °C for 4 min that results in a thermal oxide layer with the thickness of about 6 nm. The TiSi<sub>2</sub>/Si heteronanocrystals were fabricated via a two-step self-aligned silicide technique. First, the Si nanocrystals of about 20 nm in base diameters were grown on the 6 nm tunneling oxide barrier layer in a low pressure chemical vapor deposition (CVD) chamber at 600 °C for 25 s with the SiH<sub>4</sub> pressure of 200 mTorr. The dot density is about  $10^{10}$  cm<sup>-2</sup>. In the second step, a 5 nm thick metal Ti was deposited onto the sample and the first annealing was performed subsequently at the temperature of 750 °C for 3 min in nitrogen. At such relatively lowtemperature condition, the reaction between Ti and SiO<sub>2</sub> is minimized,<sup>12</sup> and Ti reacts with Si only to form the highresistive C-49 phased TiSi<sub>2</sub> (Ref. 13) on top of each Si dot. The unreacted Ti metal on top of nanocrystals as well as in between nanocrystals was removed in selective etchant (NH<sub>4</sub>OH: H<sub>2</sub>O<sub>2</sub>: H<sub>2</sub>O=1:1:5). Discrete TiSi<sub>2</sub>/Si heteronanocrystals with the same density as original Si dots were formed in this stage. The second annealing was performed also in nitrogen gas at 880 °C for 1 min after the metal removal to convert high-resistive C-49 TiSi2 to low-resistive C-54 TiSi<sub>2</sub>.<sup>13</sup> Due to fine-line effect,<sup>14</sup> only portion of C-49 TiSi<sub>2</sub> may be converted as a result of small dimension of original Si dots. Nevertheless, it is not critical to use lowresistive TiSi<sub>2</sub> phase for floating gate of memory as the work function difference between Si and TiSi2 is the dominant factor to enhance the device performance. The sample was then capped with the control oxide of about 50 nm in a lowtemperature oxide CVD furnace. Aluminum electrodes on back and front side of the sample were finally deposited and patterned to size of  $0.45 \times 0.2$  mm<sup>2</sup>. The resultant nanocrystals were characterized with scanning electron microscope (SEM) for the surface morphology and electron energy dispersive x-ray (EDX) spectroscope for the composition, respectively. The memory characteristics were investigated by Agilent 4284A LCR meter at room temperature. The memory window and time-dependent transient capacitance (C-t) were measured with capacitance-voltage (C-V) sweep at 1 MHz and constant voltage mode. Time-dependent flatband voltage shift  $(\Delta V_{\rm fb}-t)$  was deduced with LABVIEW code at constant capacitance mode.

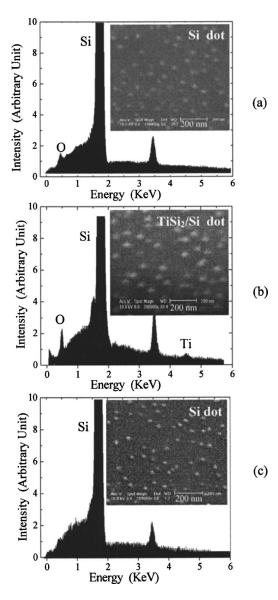

Figure 1 shows the SEM images and EDX results of the Si nanocrystals [Fig. 1(a)], the TiSi<sub>2</sub>/Si heteronanocrystals on SiO<sub>2</sub> tunneling barrier layer [Fig. 1(b)], and Si dot after TiSi<sub>2</sub> removal with 10% HF dipping [Fig. 1(c)]. One finds the dot density does not vary while the average dot size increases from  $\sim 20$  [Fig. 1(a)] to 30 nm [Fig. 1(b)], indicating the excellent self-aligned growth of TiSi<sub>2</sub> on Si dots only. The EDX result in Fig. 1(a) resolves Si and oxygen signals for Si nanocrystals on tunneling oxide. Besides these signals, the EDX result shows indeed the signal peak of Ti element

88, 103507-1

Downloaded 09 Mar 2006 to 138.23.226.140. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

<sup>&</sup>lt;sup>a)</sup>Electronic mail: jianlin@ee.ucr.edu

<sup>© 2006</sup> American Institute of Physics

FIG. 1. The characterization of the fabricated  $TiSi_2/Si$  heteronanocrystals on  $SiO_2$  thin film. SEM images and corresponding EDX spectra of Si nanocrystals (a),  $TiSi_2/Si$  heteronanocrystals (b), and Si nanocrystals after  $TiSi_2$  removal with 10% HF (c).

around 4.51 keV from TiSi<sub>2</sub>/Si heteronanocrystals, which confirms silicide formation [Fig. 1(b)]. Since the EDX signal penetration depth is of the order of 1  $\mu$ m, the Ti signal from the hetero-nanocrystals is fairly weaker than the Si signal. To confirm the nanocrystals observed in Fig. 1(b) are TiSi<sub>2</sub>/Si heterostructures rather than TiSi<sub>2</sub> nanocrystals only, diluted HF etching was used to remove TiSi<sub>2</sub>. The SEM image in Fig. 1(c) suggests that the observed smaller dots should be Si dots as no Ti signal is detected in the EDX experiment. Since diluted HF also etches SiO<sub>2</sub>, negligible oxygen signal is detected. The peaks around 1.55 keV and 3.45 keV observed in all samples are from Si substrate.

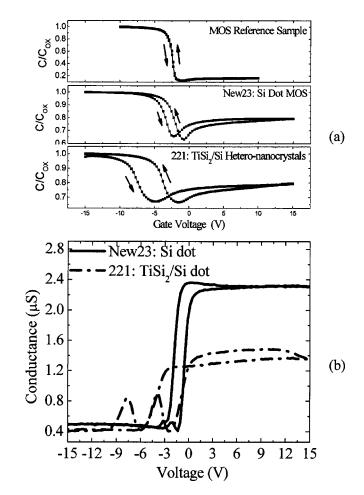

The memory effects characterized by C-V for the reference MOS, the Si dot MOS and the TiSi<sub>2</sub>/Si heterodot MOS memories are shown in Fig. 2(a), where the hysteresis feature can be found only for the Si dot MOS and the heterodot MOS capacitors after the gate voltage swept from accumulation region to inversion region and then swept back. No C-V hysteresis is found for the MOS capacitor with only tunneling oxide, but without control oxide and nanocrystals Downloaded 09 Mar 2006 to 138.23.226.140. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp

FIG. 2. C-V (a) and G-V (b) measurement results for the MOS capacitors containing TiSi<sub>2</sub>/Si heteronanocrystals and Si nanocrystals only, respectively.

embedded. Smaller minimum  $C/C_{ox}$  at high positive voltages in the reference MOS sample compared with the other two memory devices is a result of its thinner dielectric layer. The conductance-voltage (G-V) curves during the gate voltage sweep are shown in Fig. 2(b), where the similar hysteresis can be observed for both the Si dot MOS and the heterodot MOS devices. The width of the hysteresis is defined here as the memory window which indicates how obviously the flat-band voltage  $(V_{\rm fb})$  or the threshold voltage  $(V_{\rm th})$  responds to the charge injected to the nanocrystals. There are two evident differences between the Si dot MOS and the heterodot MOS in their C-V and G-V curves. First, the memory window for the TiSi<sub>2</sub>/Si heterodot MOS memory is much larger than that of the Si dot MOS memory. Second, for the heterodot MOS capacitor, the flat-band in the C-Vflank (from the accumulation region to inversion region) is shifted from the neutral device C-V curve more toward negative voltage compared with the Si dot MOS device. Since the control oxide of the two memory devices was obtained in the furnace process at the same time, relatively similar amount of fixed positive charges in the oxide and oxide thickness can be expected, which shift the C-V curves to the negative direction. Nevertheless, the ability of storing more charge in the TiSi2/Si heteronanocrystal device leads to wider memory window as it is proportional to the charge quantity in the floating dots. The C-V stretchouts in Fig. 2(a) for Si nanocrystal device and TiSi2/Si heteronanocrystal device indicate

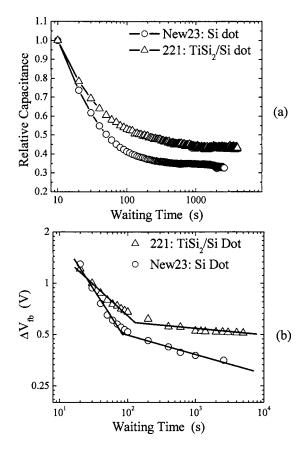

FIG. 3. Charge retention after programming at 10 V for 20 s, monitored by time-dependent transient relative capacitance (a) and flat-band voltage shift (b), respectively.

poor-quality oxide, in which fast states are generated and respond to high-frequency (1 MHz) signals.

In Fig. 3, the charge retention properties, characterized by both relative capacitance [Fig. 3(a)] and transient flatband voltage shift [ $\Delta V_{\text{fb}}$ , Fig. 3(b)], of the TiSi<sub>2</sub>/Si heteronanocrystal MOS memory are shown, where the retention curve of the Si dot device is also presented as comparison. The read voltages for capacitance are -5 V and -2.5 V for the TiSi<sub>2</sub>/Si heteronanocrystal MOS and Si nanocrystal MOS, respectively, which are within the corresponding memory windows. The relative capacitance is defined as  $|C(t)-C_N|/|C_W-C_N|$ , where C(t),  $C_N$ , and  $C_W$  are the capacitance at time t, the capacitance of the neutral device and the capacitance right after the writing operation, respectively.  $\Delta V_{\rm fb}$  is obtained by comparing the C-V curves from a charged state and the quasi-neutral state. The retention measurements were performed immediately after programming the devices by applying a voltage of 10 V on the gate for 20 s. The decays of both the transient capacitance and  $\Delta V_{\rm fb}$ for the TiSi<sub>2</sub>/Si heteronanocrystal MOS device are slower than those of the Si dot device. It is evident that the  $\Delta V_{\rm fb}$ decay of both heterodot device and Si dot device are stepwise decline functions, each including two decay mechanisms with different decay time constant. The two time constants are 1.42 and 0.114/decade for the Si dot device (No. New23) and 0.849 and 0.0154/decade for TiSi<sub>2</sub>/Si heteronanocrystal device (No. 221), respectively. The faster decay procedures for both Si nanocrystal and TiSi2/Si heteronanocrystal devices in the earlier retention stage are believed to arise from poor-quality tunneling oxide, which induces leaky paths and shallow defect-related charge traps. Electrons trapped in those sites are easier to leak back to the substrate. The slower processes in the later retention stage for these two devices are due to the deeper levels in/on Si dots and the ground energy levels of the silicide dots that are much lower than the conduction-band edge of the substrate. It is noted that the decay constant in the later retention stage of the Si dot device, indicating significantly improved charge retention ability of  $TiSi_2/Si$  heteronanocrystal memory over Si nanocrystal memory.

It should be mentioned that the retention times of both the Si nanocrystal and  $TiSi_2/Si$  heteronanocrystal MOS memories are quite short. This is primarily attributed to the poor quality of the tunneling oxide, which contains a large amount of defects and favors the leakage via trap-assisted tunneling. However, the device performance improvement by using  $TiSi_2/Si$  heteronanocrystals to replace Si nanocrystals has been demonstrated with the same poor-quality tunneling oxide. With optimized thermal oxide, it is expected that better retention performance can be achieved for these devices.

In summary,  $TiSi_2/Si$  heteronanocrystals were fabricated successfully by using the salicide technique on Si nanocrystals resting on silicon oxide films. The MOS capacitor containing these heteronanocrystals exhibits 7.5 times improved charge retention characteristics while also possesses a wider memory window as compared to the Si nanocrystal memory device. It is promising to use  $TiSi_2/Si$  heteronanocrystals to replace Si nanocrystals for the next generation floating gate flash memory devices.

The authors acknowledge the financial and program support of the Microelectronics Advanced Research Corporation (MARCO) and its Focus Center on Function Engineered NanoArchitectonics (FENA).

- <sup>1</sup>S. Tiwari, F. Rana, K. Chan, L. Shi, and H. Hanafi, Appl. Phys. Lett. **69**, 1232 (1996).

- <sup>2</sup>Q. Wan, C. L. Lin, W. L. Liu, and T. H. Wang, Appl. Phys. Lett. **82**, 4708 (2003).

- <sup>3</sup>Z. Liu, C. Lee, V. Narayanan, G. Pei, and E. C. Kan, IEEE Trans. Electron Devices **49**, 1606 (2002).

- <sup>4</sup>C. H. Lee, J. Meteer, V. Naraysnsn, and E. C. Kan, J. Electron. Mater. **34**, 1 (2005).

- <sup>5</sup>J. J. Lee and D. L. Kwong, IEEE Trans. Electron Devices **52**, 507 (2005).

- <sup>6</sup>T. C. Chang, P. T. Liu, S. T. Yan, and S. M. Sze, Electrochem. Solid-State Lett. 8, G71 (2005).

- <sup>7</sup>S. Choi, S. S. Kim, M. Chang, H. S. Hwang, S. H. Jeon, and C. W. Kim, Appl. Phys. Lett. **86**, 123110 (2005).

- <sup>8</sup>J. H. Chen, W. J. Yoo, D. S. H. Chan, and L. J. Tang, Appl. Phys. Lett. **86**, 073114 (2005).

- <sup>9</sup>Y. H. Lin, C. H. Chien, C. T. Lin, C. Y. Chang, and T. F. Lei, IEEE Electron Device Lett. **26**, 154 (2005).

- <sup>10</sup>S. Y. Huang, K. Arai, K. Usami, and S. Oda, Nanotechnology **3**, 210 (2004).

- <sup>11</sup>M. Sadd, J. A. Yater, J. Bu, C. M. Hong, W. M. Paulson, C. T. Swift, R. Singh, L. Parker, and M. G. Khazhinsky, in *Proceedings of the IEEE Non-Volatile Semiconductor Memory Workshop*, Monterey, CA, 16–20 February 2003 (IEEE, New York, 2003), p. 71.

- <sup>12</sup>Y. Koh, F. Chien, and M. Vora, J. Vac. Sci. Technol. B 3, 1715 (1985).

- <sup>13</sup>I. D. Wolf, D. J. Howard, A. Lauwers, K. Maex, and H. E. Maes, Appl. Phys. Lett. **70**, 2262 (1997).

- <sup>14</sup>R. A. Roy, L. A. Clevenger, C. Cabral, Jr., K. L. Saenger, S. Brauer, J. Jordan-Sweet, J. Bucchignano, G. B. Slephenson, G. Morales, and K. F. Ludwig, Jr., Appl. Phys. Lett. **66**, 1732 (1995).

Downloaded 09 Mar 2006 to 138.23.226.140. Redistribution subject to AIP license or copyright, see http://apl.aip.org/apl/copyright.jsp